Generación de una onda sinusoidal en un gran rango de frecuencia

Greg de Eon

Quiero construir un circuito que pueda generar ondas sinusoidales a frecuencias controladas por una computadora o un microcontrolador. Me gustaría ir tan bajo como 0,01 Hz (probablemente hasta 0,05 Hz sería aceptable) y tan alto como 100 kHz; Necesito al menos 10 frecuencias por década, que es una resolución de aproximadamente 12 MHz en la parte inferior de la escala (o 60 MHz si la parte inferior es de 0,05 Hz). El voltaje de salida no necesita ser alto; de todos modos, después lo pasaré por algunos amplificadores operacionales.

¿Cuál es la forma estándar de hacer esto? ¿Es DDS el camino a seguir (utilizando una tabla de búsqueda de seno en un uC o un IC como el AD9850)? ¿Hay una solución analógica simple que me falta?

Me encantaría ceñirme a las partes de orificio pasante si puedo.

Respuestas (4)

mercado

Podría hacer fácilmente un DDS altamente flexible en una placa Discovery STM32F4 por ~ $ 15 usando un DAC interno, DMA, un temporizador y una tabla de búsqueda de seno. La gente ha blogueado ejemplos de cosas similares si las buscas.

Para obtener la frecuencia requerida (los DAC STM32F4xx solo pueden hacer 300ksps a pleno rendimiento, lo que equivale a ~1V/ s) deberá restringir el rango del DAC.

Para una sinusoide, la velocidad de respuesta máxima (en V/s) es . Insertando los valores de los requisitos del OP y suponiendo que Vref del DAC es de 3,3 V (que, si recuerdo correctamente, es el caso de un STM32F4Disco), una onda sinusoidal de 3,3 Vpp a 100 kHz, la velocidad de giro máxima es V/s, o V/ s.

Para cumplir con esta restricción, la amplitud de la onda sinusoidal tiene que ser limitada, de V a v

Esto ahora trae el problema aparente del límite de 300 ksps en el DAC STM32F4. Ese límite es un furphy. No sé cuál es el límite superior físico real, pero sospecho que es la velocidad del bus APB1. Sé (porque lo he hecho) que puede escribir al menos 2Msps en el DAC y, siempre que respete la velocidad de respuesta de 1V/us, se comportará de manera predecible. Por lo tanto, puede hacer 16 muestras por ciclo para una onda sinusoidal de 100 kHz, una tasa de actualización de 1,6 Msps, siempre que limite la amplitud de la onda sinusoidal a 3,18 V en lugar de 3,3 V.

En algún momento, probablemente tendrá que lidiar con potenciómetros digitales porque la realidad es que si desea una señal de salida continua y suave, especialmente a baja velocidad, entonces tendrá que pasar su DDS por un filtro, y ese filtro tendrá que ser ajustable: no puede simplemente ponerle un LPF de 100 kHz y esperar que sea útil en frecuencias inferiores a 1 Hz.

Greg de Eon

Jorge Herold

mercado

Jorge Herold

mercado

Efervescencia

Efervescencia

mercado

Nicolás D.

mercado

Efervescencia

Pelusa regenerada

Aquí está mi (RF) resumen aproximado de la solución DDS, que inicialmente fue sugerido por Nick Alexeev. Estoy marcando esto como wiki de la comunidad, así que siéntete libre de mejorar con detalles, etc.

Usando la calculadora de AD , para obtener el equilibrio deseado entre la resolución de frecuencia de 12 MHz (que simplemente redondearé a 10 MHz) y una curva resnoblemente suave a una salida de 100 KHz, necesita un reloj DDS de 10 a 40 MHz, con 20 MHz que parece un buen término medio Con un reloj inferior a 10Mhz, la salida del DDS a 100KHz comienza a parecer bastante ruidosa. En relojes superiores a 40Mhz, la resolución se vuelve demasiado gruesa; con un reloj de 40 MHz, obtiene un cambio de poco menos de 0,01 Hz por cada bit de sintonización, en el rango bajo, por supuesto; siendo la palabra de sintonización un divisor de reloj, produce una curva de frecuencia no lineal.

En cuanto a las soluciones prácticas, uno puede encontrar chips DDS ya montados en protectores compatibles con Arduino (parece que cuestan alrededor de $ 5); Sin embargo, el problema es que pueden venir con un reloj fijo (y posiblemente inadecuadamente alto), pero eso se puede mejorar con un poco de trabajo en el tablero.

También vale la pena mencionar que si uno está usando un microcontrolador (uC) que tiene un DAC incorporado y lo suficientemente rápido, entonces agregar un DDS (que es básicamente un ASIC que barre una tabla de búsqueda sinusoidal y envía ese valor indexado a un DAC) es bastante inútil ya que la búsqueda de seno se puede implementar en el software uC. Para obtener más detalles sobre este enfoque de DAC integrado, consulte la respuesta de Markt.

Andy alias

He usado un diseño para un oscilador no digital que produce senos decentes por debajo de 0,1 Hz y por encima de 100 kHz. En teoría, era un circuito sintonizado en paralelo LC en la ruta de retroalimentación de un amplificador. La L y la C eran en realidad circuitos giratorios de precisión (es por eso que podían sintonizarse a frecuencias de resonancia tan ridículamente bajas). Nunca construiría uno con inductores reales y, si lo hiciera, no sería sintonizable.

Tanto "C" como "L" se mantuvieron en seguimiento mediante el uso de un potenciómetro de doble banda de precisión y, si no recuerdo mal, se podía obtener un rango de frecuencia de más de 50:1 del potenciómetro antes de cambiar los condensadores fijos en los giradores.

Los potes, por supuesto, estarían mejor atendidos por digipots en estos días, ya que estos pueden "seguir" mucho mejor que los potes normales. Estoy seguro de que con cuidado, podría funcionar hasta 0,01 Hz.

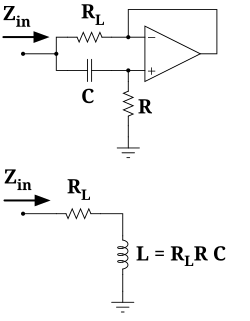

Inductor giratorio: -

Hay giradores de mayor calidad (mejor respuesta de frecuencia) y aquí hay otro enlace a un documento sobre un tipo diferente de girador. La belleza del girador de amplificador operacional único en esta aplicación es que la red CR (como normalmente se pretende que sea parásita) se puede usar de manera efectiva como la sección de sintonización que hace que L y C estén en paralelo a través de resistencias en serie pequeña.

Greg de Eon

Andy alias

Greg de Eon

Efervescencia

Andy alias

Greg de Eon

Andy alias

Efervescencia

Efervescencia

steverino

Un enfoque sería sincronizar un sumador/acumulador de 28 bits con un reloj de 4 Mhz. Un uController maneja los 20 bits de orden bajo con una palabra digital y los ocho bits superiores alimentan direcciones a un eprom para una tabla de búsqueda de seno de 256 entradas. Los bits de datos del eprom sumados en una escalera R2R se acoplarían capacitivamente a la etapa de ganancia de su amplificador operacional. Conduzca un valor alto del micro al sumador y los bits de alto orden se ciclan más rápido, para una onda sinusoidal de mayor frecuencia. Un valor bajo requiere mucho más ciclo de reloj para hacer un conteo en los ocho bits superiores que impulsan el eprom. Con un poco de trabajo extra en el microsoftware; puede hacer que la tabla eprom sea más pequeña simplemente almacenando ángulos desde 0 grados hasta 90. Simplemente lea la tabla hacia adelante para los primeros 90 grados (cuadrante 1) y luego hacia atrás para el cuadrante 2 hacia adelante nuevamente para el cuadrante tres, etc.

Efervescencia

steverino

Efervescencia

Greg de Eon

¿Puedo cambiar 85V / 3kHz CA usando este relé de estado sólido?

Distorsión de onda sinusoidal en un circuito de amplificador operacional simple: ¿condensador de derivación?

Compré un acondicionador de aire en Tailandia clasificado 220v-240v, 50 Hz. ¿Qué podría pasar si lo uso en nuestro país que usa 220v, 60 Hz? [cerrado]

¿Qué tan precisa es la frecuencia de los enchufes de pared de EE. UU.? [duplicar]

¿Cómo construir un circuito que genere una onda sinusoidal?

Circuito para encontrar las RPM del motor usando el cable de tierra de la bobina del magneto

¿Cómo puede un cable telefónico tener múltiples frecuencias a la vez?

¿Qué tan precisa es la frecuencia de la red eléctrica de CA?

Bias-tee para agregar múltiples frecuencias a una línea de CC

¿Cómo obtenemos la frecuencia compleja de una función sinusoidal amortiguada exponencialmente?

Nick Alexeev

Jorge Herold

Efervescencia

Greg de Eon

Efervescencia

Greg de Eon

Greg de Eon