Topología de suministro de 3 V y 5 V (diseño integrado, señal mixta)

usuario49118

Estoy desarrollando un sistema integrado de señal mixta que requiere rieles de 5V y 3V.

El riel de 5V alimenta un sensor analógico y un ADC de precisión. La naturaleza del sensor es tal que su salida será CC la mayor parte del tiempo y cambiará lentamente el resto del tiempo. El bajo nivel de ruido y el bajo coeficiente de temperatura son los aspectos más importantes de este riel.

El riel de 3 V alimenta el circuito digital (interfaz digital ADC, MCU (comunicaciones SPI y UART), módem). Hay dos esclavos SPI: el ADC y un DAC. El ruido, tempco y regulación de este carril no son críticos. El bajo costo es lo más importante.

El ADC está muestreando continuamente, las transacciones SPI son periódicas y la comunicación UART es bajo demanda (y poco frecuente). El oscilador interno del microcontrolador funciona a 1 MHz y está sincronizado con un cristal de reloj de 32768 Hz.

Debe haber un amplio rango de voltaje de entrada (10 - 40 V CC). Por esta razón tengo la intención de utilizar LDO de tres series; el primero se conectará a la entrada y generará 5.5V. El motivo de 5,5 V es que el suministro de 5 V tiene un voltaje de caída de 200 mV, que debe mantenerse en un amplio rango de temperatura.

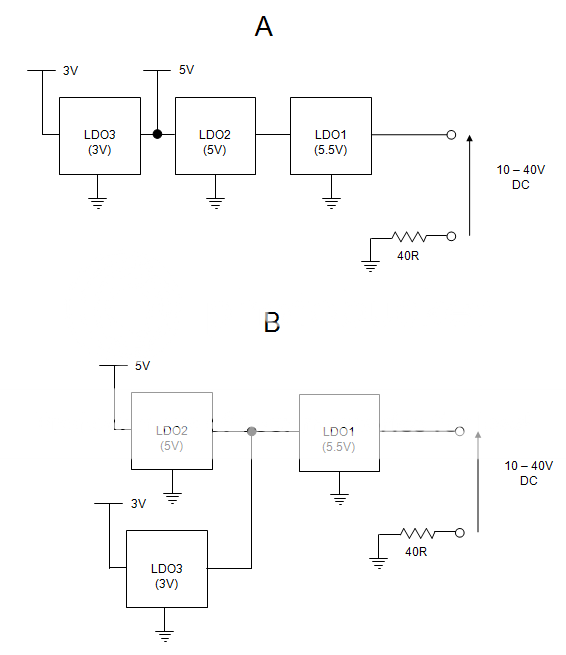

Este riel de 5,5 V alimentará a los otros dos LDO. En la siguiente imagen se muestran dos formas de lograr esto (la resistencia de 40 ohmios es parte integral de un circuito integrado; toda la corriente del circuito fluye a través de él):

Con referencia a la imagen, evalúe la veracidad de las siguientes afirmaciones:

1) La topología B es muy superior, incluso si los suministros se desvían bien, ya que los cambios en la demanda seguirán teniendo algún efecto en la regulación de la carga del riel de 5V.

2) No hay mucha diferencia entre las topologías A y B, si los suministros están bien puenteados y el riel de 5V tiene una buena regulación de carga.

3) Las declaraciones 1) y 2) no pueden evaluarse significativamente sin más información sobre el sistema y los componentes.

4) El mayor efecto, con mucho, se debe al esquema de conexión a tierra (por ejemplo, conexiones a tierra en cadena de vuelta a la resistencia de 40 ohmios en lugar de una configuración en estrella).

5) Ambas topologías son una forma extraña/ineficiente de lograr el objetivo. Hay soluciones que son mucho mejores en términos de costo y rendimiento.

6) Esta pregunta muestra una falta de comprensión.

EDITAR: 7) Los LDO generalmente son mejores para lidiar con la variación de línea que con la variación de carga. Entonces, si bien la topología B podría tener más efecto en el riel de 5,5 V, el LDO de 5 V manejará esto mejor que si hubiera un efecto en su carga (como ocurre en la topología A).

EDITAR: Para aclarar, el circuito es de baja potencia: solo se extraen 3.1 mA en total de la entrada.

Respuestas (1)

Spehro Pefhany

B es mejor: no está inyectando ruido digital directamente en su suministro analógico de precisión.

Podría ser incluso mejor extraer el suministro de 3,3 V directamente del suministro de entrada. Por ejemplo, un solo BJT (seguidor de emisor) del regulador de 5,5 V le dará un poco menos de 5 V de salida, que su LDO de 3,3 V puede manejar fácilmente (suponiendo que no pueda manejar 40 V directamente). Eso también reducirá la disipación en el LDO de 5.5 V (¿realmente tiene que llamarlo tan cerca y realmente necesita un LDO en esta posición?).

usuario49118

usuario49118

Spehro Pefhany

usuario49118

usuario49118

Fuente de alimentación de +5V y -5V de 12V DC

Conecte la fuente de alimentación de CA/CC a varios dispositivos

Reduzca 20 V CC a 9 V CC

¿Estamos cerca de un hogar DC puro (o híbrido)? [cerrado]

¿El diámetro de la bobina de un motor determina la cantidad de voltios necesarios para hacerlo funcionar? [cerrado]

LNK306 5V 300mA

¿Puedo combinar la fuente de alimentación?

Alimentación de 4,6 V con fuente de alimentación USB de 5 V

Fuente de alimentación de CA a CC: capacitancia de tierra en la salida de CC

Multisim - Luchando con un circuito de suministro de energía

chico funky

pedro bennett

Campos EM

usuario49118

usuario49118

usuario49118

usuario49118